Journal of Engineering Research and Reports

23(3): 50-56, 2022; Article no.JERR.90992 ISSN: 2582-2926

### Validation of New Substrate Design for the Improvement of Strip Warpage on LGA Packages

Jerome Dinglasan<sup>a\*</sup> and Mariane Mendoza<sup>a</sup>

<sup>a</sup> STMicroelectronics, Inc., Calamba City, Laguna-4027, Philippines.

Authors' contributions

This work was carried out in collaboration between both authors. Both authors read and approved the final manuscript.

Article Information

DOI: 10.9734/JERR/2022/v23i317600

**Open Peer Review History:**

This journal follows the Advanced Open Peer Review policy. Identity of the Reviewers, Editor(s) and additional Reviewers, peer review comments, different versions of the manuscript, comments of the editors, etc are available here: https://www.sdiarticle5.com/review-history/90992

Original Research Article

Received 19 June 2022 Accepted 23 August 2022 Published 29 August 2022

### ABSTRACT

Land grid array or LGA package of semiconductor has been commonly used on our modern technology, from home gadgets up to industrial uses. Improvements to correct product defects and process issues are introduced to have quality products for customer satisfaction. Substrate warpage have been affecting production performance on semiconductor manufacturing. The unacceptable response results to loss of productivity losses and yield detraction. Different process improvements have been experimented to contain the problem, but results are not maintained and found to be not robust. This is where design innovation plays the part. Solder mask opening on the base material of the substrate is considered to have a favorable response after subjecting it to different environment conditions. From fast indexing and machine movement up to high thermal application on oven curing, having a robust solder mask design makes the unit acceptable and with quality. Product design as mentioned takes on another level to address the phenomenon of substrate warpage. This manuscript will be discussing how the solder mask of the substrate is optimized to achieved minimal or zero substrate warpage by performing different experiments on process and the product itself. Statistical analysis has been the basis for the implementation of the newly validated substrate design.

Keywords: Front-of-line; land grid array; MEMS; solder mask opening; substrate design; warpage.

\*Corresponding author: Email: jerome.dinglasan@st.com;

### **1. INTRODUCTION**

In the fast-pacing technology and innovation all around the globe, every industry strives for limitless and continuous improvement. Companies with manufacturing plants, services and labor demands on the open market are seizing all opportunities for a better product that customers expect on them. Semiconductor industry is one of the leading examples who projects modern technology and miniaturization on their products. From enormous size of integrated circuits or ICs to nano size processors that can be found on advanced gadgets we use every single day of our lives. Every individual is committed to achieve satisfaction and quality of their products and services [1-4].

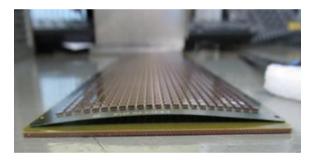

On the semiconductor package of LGA's or Land Grid array for micro electromechanical system products, substrate warpage is one of the challenges the manufacturing faces and experience. Substrate warpage as seen on Fig. 1 is the reaction of the material to "bend" or warp after subjecting to oven curing process.

## Fig. 1. Warpage visible on substrate after oven curing

High warpage that is already evident after oven curing as shown on Fig. 1 is no longer acceptable on the succeeding process step of wire bonding. The warpage measurement acceptance is 1.2mm altitude from the flat surface but the measurement after oven curing is found to be 4.0mm. At time zero, the strip warpage measurement is already at 2.4mm and is already out of acceptance criteria. Based on previous research cited on [5-7] substrate modeling is used to simulate the potential measurement warpage and how it may potentially affect downstream process. It was mentioned also on [8] the improvement of applying heat via oven curing to reduce warpage and have acceptable materials for the next processes. With these research and studies, authors of this manuscript have found an

opportunity to study the problem and explore solutions that can be offered related on the substrate revisions.

### 2. REVIEW OF RELATED LITERATURE

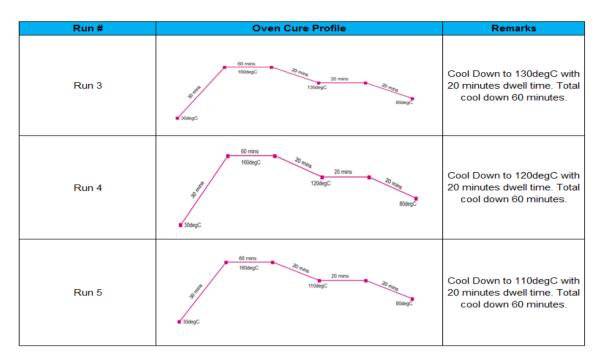

Substrate warpage is one manufacturing issues that were unexpectedly encountered by manufacturing engineers. There are several factors that affect this substrate warpage. Based on the research cited on [9], temperature during oven curing of products is one of factors considered. Several evaluations to use different cuing profile were performed and based on specific material affected, best curing profile was defined. as seen on Fig. 2 from the same citation [9] sample of design of experiments on different temperature profile that contributes to substrate warpage, and its effect.

Other studies performed process improvements by applying weights on the material during heat application. Weights will control the movement of substrate by applying opposing force on the direction of the warpage. This practice as discussed on [10] has been applied and effective on other products but not all results were favorable. That is why the design improvement and modification of core materials is put into play to have robust resolution.

### 3. METHODOLOGY

Supported by various research and the related literatures as discussed on [11-13], the authors first aim to measure warpage from time zero and see how the measurement behaves as the process progresses at front-of-line (FOL) stations. Shown on Fig. 3 is the FOL Process flow generated specifically for this activity where the authors will verify the warpage measurement step-by-step. This includes oven curing of substrate without die and oven curing after die attach.

Once strip behavior is comprehended using this process flow, the authors have recommended to validate distinctive designs of solder mask opening (SMO) as consulted and recommended from the supplier. Validation includes the parallel run of the existing SMO design versus the modern designs recommended by the supplier as the SMO design affects the warpage measurement. With this activity, we can compare the performance of both materials and produce a strategic plan to perform the evaluation. Upon result availability, the authors would conclude the best design to demonstrate low warpage measurement given with data results and statistical analysis.

### 4. RESULTS AND DISCUSSION

### 4.1 Measurement of Strip Warpage for Every FOL Process Steps

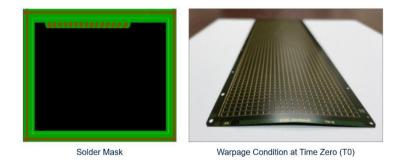

Existing design of substrates has its SMO around each of every unit in the strip. Shown on Fig. 4 is the reference substrate design illustration and the warpage condition at Time Zero (T0). At T0, warpage measurement is found with average of 1.6 mm.

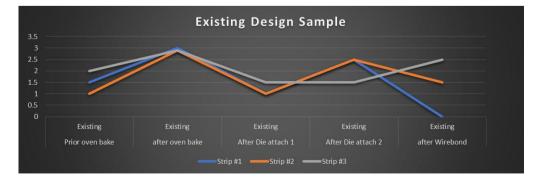

The oven profile of the die attach material used by the product have specific timing and curing temperature known as ramp up, dwell and cool down. These three factors as cited on [14-15] helps the strip to have desirable response of attached die, and substrate condition. Upon process application, the warpage measurement increases when applied with heat along the processes. Curing and cooling helps the strip to be flattened but must meet the target of 1.2mm acceptance warpage altitude of the next process which is wire bonding. This measurement may also result to other problems at wire bond like depressed wire or damaged substrate. As shown on Fig. 5 is the behavior of the strip warpage along the process. Three strips were used to validate the warpage results of the existing design of the strip.

With the behavior observed on the existing strip, there will be in need for a drastic improvement from the design level of the core material. the authors have proceeded to assess the recommended innovative designs of substrates aiming to reduce the warpage with respect to the curing time and temperature of the product, and to avoid issues on the next process steps at FOL.

### 4.2 Identification of the New Designs of Substrates

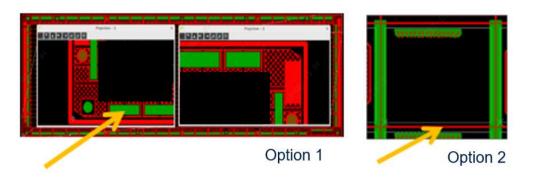

With the result of the existing substrate design validation performed using several strips, two recommendations were given by the supplier and was considered for evaluation. One modification called as the Scheme 1 pertains to the whole strip where the SMO design is changed on the bottom strip rail, aiming to control the whole warping of the strip. Another modification called as the Scheme 2 pertains to the SMO design changed per unit where gold plated bars were covered by SMO on the long side of the strip. Both designs are shown on Fig. 6.

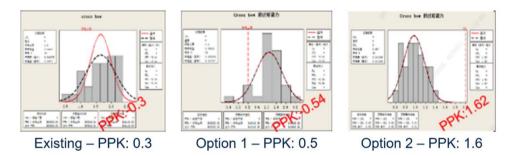

Simulation of both designs at supplier side shows that Option 1 cannot be longer considered as it has no improvement from the existing design. On the other hand, Option 2 proceeded into validation on the assembly line as progress is evident on the simulated results from the supplier. Shown on Fig. 7 is the process probability measure for both designs shown that Option 1 is not recommended for further validation and Option 2 can proceed with further analysis.

With the data on hand, the authors concurred to continue the validation run of the substrate design of Option 2 which has the higher process capability from the two. Parallel run for existing and considered innovative design will be verified.

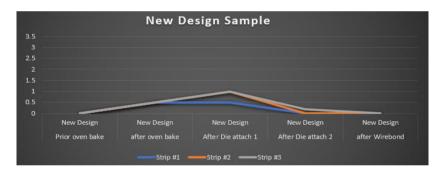

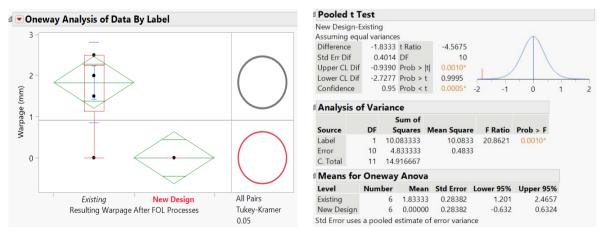

# 4.3 Validation Run between Existing and New Substrate Designs

Then new design of substrate from Option 2 is used for validation at FOL. Warpage was measured at every process step as gathered on the existing design. Fig. 8 shows that the warpage of the strips has different and improved response where maximum warpage measured is only 1.0 mm. Statistical test using One way analysis shown on Fig. 9 indicates that there is a significant difference with a P-value of 0.0010 based on the performance between the existing and the new substrate designs with showing that the new substrate design has the lower and favorable results in terms of warpage measurement.

Additional evidence shown that the study and measurement is valid as warpage was evident on sample photos shown on Figs. 10 and 11. Fig. 10 is the progress of warpage along the process for existing design from zero to 3.0 mm, while Fig. 11 shows the progress from new substrate design having a substrate warpage of 1.0mm maximum.

Data from the evaluation and statistical analysis results show that the substrate design validation described on the methodology is suited for the identification of the acceptable substrate warpage response. With the correct interpretation to choose the best option, it will be a tremendous help to determine the acceptable response for a robust quality product. Dinglasan and Mendoza; JERR, 23(3): 50-56, 2022; Article no.JERR.90992

### Fig. 2. Design of experiment of different oven curing profile

### Fig. 3. Design of experiment of different oven curing profile

Fig. 5. Existing design warpage measurement per process step

Dinglasan and Mendoza; JERR, 23(3): 50-56, 2022; Article no.JERR.90992

Fig. 6. Improved substrate designs for evaluation from substrate supplier

Fig. 7. Process performance between existing and new substrate designs

(9a)

(9b)

Fig. 9(a, b). Statistical study results

Existing Design of Substrate Results

#### Fig. 10. Existing substrate validation photos

New Design of Substrate Results

### Fig. 11. New substrate validation photos

### 5. CONCLUSION AND RECOMMENDA-TIONS

It has been concluded that the existing substrate design have warpage issues that is related with the SMO. Out of the two new designs recommended by the supplier, it was found out that Option 2 has the most significant result to lower down the warpage but limited and applicable on Front-of-line processes of semiconductor industry. It was noted also that the design of Option 2 with SMO covering the gold-plated bars at the long side of the strip improves the warpage measurement significantly. Studies and research added on the references from other manufacturing is considered significant help to assess and conduct experiments related to die attach oven curing.

In parallel, the authors recommend in consideration of the Option 2 Design of Substrate to lessen the warpage measurement. It is also recommend that the validation made on this study to monitor and understand the warpage behavior to verify the design effectiveness.

### ACKNOWLEDGEMENT

The authors would like to thank Gilman Jimenez for the substrate supplier interface communi cation, Marciano Maniebo for the simulation at Wirebond process, Gemma Balicao for engineering samples coordination, and to the whole Operations One Pre-Production Group.

### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

### REFERENCES

1. Chang-Chun Lee, Chia-Chi Lee, Che-Pei Chang. Simulation methodology development of warpage estimation for epoxy molding compound under considera -tions of stress relaxation characteristics and curing conditions applied in semiconductor packaging, Materials Science in Semiconductor Processing. 2022;145(106637).

ISSN:1369-8001.

Available:https://doi.org/10.1016/j.mssp.20 22.106637

- Mendoza MA, Buera MVS, Gomez FRI & Kumawit AJD. Understanding jig align ment error occurrences for substrate 1map strips. Journal of Engineering Research and Reports. 2021;20(9):113-118. Available:https://doi.org/10.9734/jerr/2021/ v20i917380

- Kenny S, Baron D, Roelfs B and Bruening F. A comprehensive packaging solution for next generation ic substrates. Microelectronics and Packaging Conference (EMPC) 2011 18<sup>th</sup> European. 2011;1-4.

- 4. Lee YS, Lin PY, Wu KT, Lee HH and Hwang SJ. Effects of substrate structure on the warpage of flip chip ic packages. 13th International Microsystems, Packaging, Assembly Circuits Technology Conference and (IMPACT). 2018;66-70. DOI: 10.1109/IMPACT.2018.8625738

- Lien C, Chuang Y, Yao Y, Charn E and Chen E. Block-based finite element modeling, simulation, and optimization of the warpage of embedded trace substrate. 2018 IEEE 20th Electronics Packaging Technology Conference (EPTC). 2018; 802-806,

DOI:10.1109/EPTC.2018.8654342

Wang M and Wells B. Substrate trace modeling for package warpage simulation.

2016 IEEE 66th Electronic Components and Technology Conference (ECTC). 2016;516-523.

DOI:10.1109/ECTC.2016.199

- Talledo J. Modeling of leadframe strip warpage after die attach cure process. Journal of Engineering Research and Reports. 2021;20(3):50-56. Available:https://doi.org/10.9734/jerr/2021/ v20i317281

- Michael Capili D and Frederick Ray Gomez I. Redefining substrate pre-bake method for strip warpage improvement. International Research Journal of Advanced Engineering and Science, 2019; 4(3):155-157.

- 9. Tito Mangaoang T Jr, Jerome Dinglasan J, Jefferson Talledo S. Manufacturing challenges on thin and coreless (Philippines substrates. PSECE Semi conductor & Electronics Convention & Exhibition); 2016.

- 10. Arnold Rada, Bong Cabading, Ela Mia Cadag. A systematic approach in optimizing strip warpage of an ultra-thin flat no lead (QFN) package. 1-5.

- 11. Graycochea Jr, Gomez EM, FRI, & Rodriguez RS. Warpage mitigation through diebond process improvement with

enhanced leadframe configuration. Journal of Engineering Research and Reports. 2020;10(2):39-42. Available:https://doi.org/10.9734/jerr/2020/ v10i217035

- 12. Chen TY and Shin MK. Extremely low warpage coreless substrate for sip module. IEEE 18th Electronics Packaging Techno logy Conference (EPTC). 2016;89-92. DOI:10.1109/EPTC.2016.7861449

- Jonathan Pulido C and Frederick Ray Gomez I. Warpage improvement at wirebond assembly process of semiconductor QFN device. International Research Journal of Advanced Engineering and Science. 2019;4(3):332-333.

- Beh KS et al. Finite element analysis of substrate warpage during die attach process. Int'l Symposium on Electronic Material and Packaging. 2002;94-98.

- 15. McCaslin and Sitaraman L SK. Methodology modelina for substrate warpage using copper trace pattern implementation. Electronic. 58th Components and Technology Conference, 2008;1582-1586. DOI:10.1109/ECTC.2008.4550187

© 2022 Dinglasan and Mendoza; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

> Peer-review history: The peer review history for this paper can be accessed here: https://www.sdiarticle5.com/review-history/90992